# SDMay19-41

Brian Bradford Jared Danner Nick Knuth Vishal Joel Louis Hamilton

### **High-Level Requirements**

- Porting of the CASPER spectrometer application to the ZCU111 and RFSoC

- Integration of Migen into the CASPER tooflow

- Extending of PYNQ to work with the tooflow

### Use Case

• The CASPER community has reached out to developers to integrate Xilinx's new RFSoC platform into their current tools. Once supported, anyone making use of their open-source tools will be able to quickly develop digital instrumentation for their specific applications.

# Functional & Non-functional Requirements

- Functional

- CASPER spectrometer support

- **Z**CU111 must be made to support the CASPER spectrometer and the DSP libraries that it is dependent on.

- Migen

- Must be able to auto-generate HDL from CASPER modules, create a corresponding Vivado project and generate a bitstream targeting the ZCU11

- Spectrometer

- Parameterized inputs allow users to quickly configure the application for different use cases

- Non-functional

- Backwards compatibility

- The ability to still use MATLAB/Simulink and existing CASPER Toolflow along with Migen to program the board.

- Open source

- Anyone can use our code in their application.

- IEEE Standards

- 211-1997<sup>TM</sup> IEEE Standard Definitions of Terms for Radio Wave Propagation

- 1241-2010<sup>TM</sup> IEEE Standard of Terminology and Test Methods for Analog-to Digital Converters

- 802.3<sup>TM</sup> IEEE Standards for Ethernet

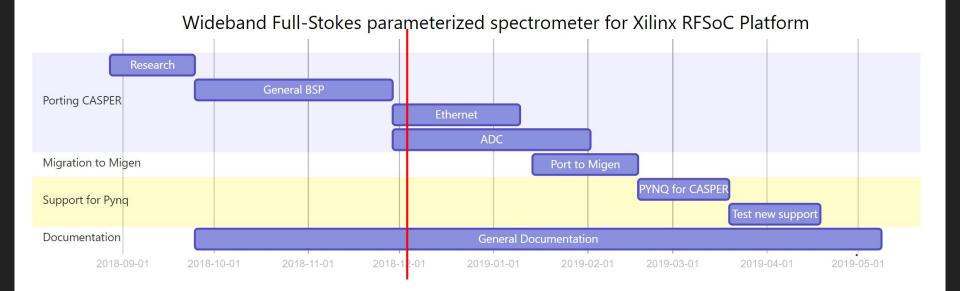

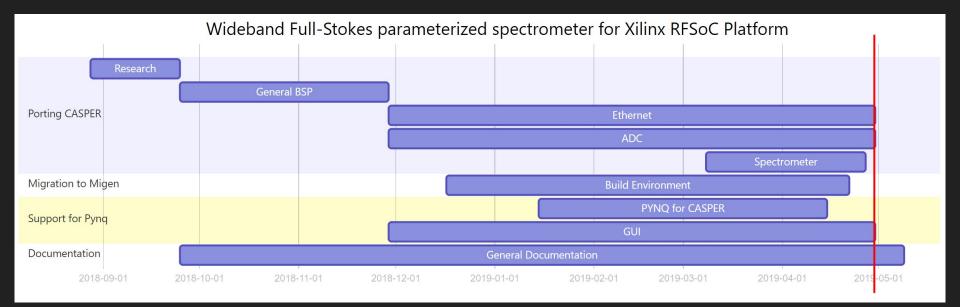

## Design Plan

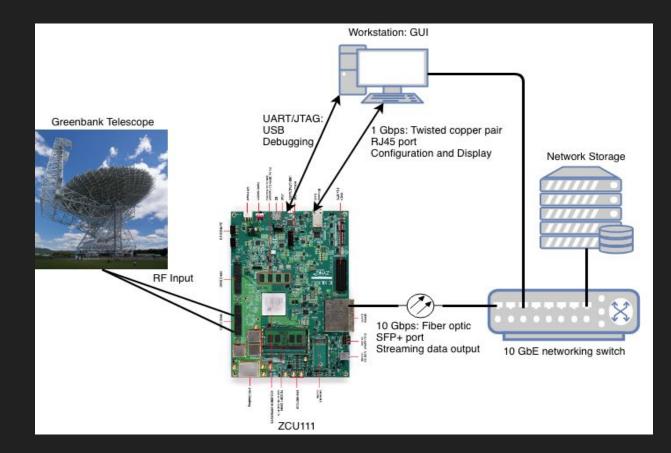

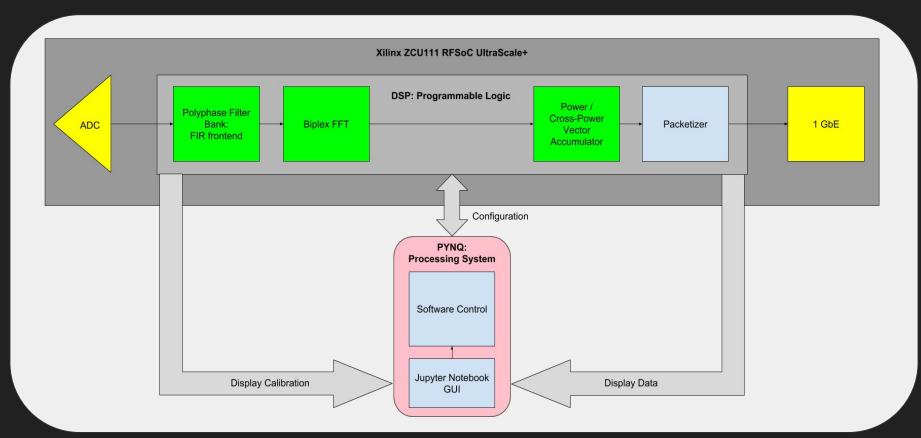

- Designing an ADC, spectrometer, ethernet module to port CASPER's spectrometer instrument to the ZCU111.

- The board infrastructure was designed using Migen and PYNQ.

- Migen was used as an experimental tool to test whether it would be a viable option to replace the existing CASPER toolflow.

- PYNQ interfaced with the modules in order to provide register software access.

- Create a GUI in Jupyter Notebooks to provide an interface for the entire spectrometer application, which allows for

- Quick configuration of various spectrometer parameters

- Effectively display data from various sections of the system

# **Design Objectives**

- Porting of the CASPER spectrometer instrument and dependent libraries to the Xilinx ZCU111 evaluation platform.

- General board support

- Ethernet interface

- ADC interface

- Migrating the current CASPER Toolflow to use Migen, an open source python library for generating and building gateware projects.

- Support for Xilinx PYNQ infrastructure, which will interface to existing CASPER Python libraries.

- Documentation of project for future users: source code, gateware, and firmware descriptions.

### System Constraints

- CASPER spectrometer support

- ZCU111 board must be made to support the CASPER spectrometer and the libraries it is dependent on.

- Migen

- Must be able to auto-generate HDL from CASPER modules, create a corresponding Vivado project and generate a bitstream targeting the ZCU111

- Backwards compatibility

- The ability to still use MATLAB/Simulink and existing CASPER Toolflow along with Migen to program the board.

- Open source

- Anyone can use our code in their application.

- IEEE

- 211-1997 IEEE Standard Definitions of Terms for Radio Wave Propagation

- 1241-2010 IEEE Standard of Terminology and Test Methods for Analog-to Digital Converters

- 802.3 IEEE Standards for Ethernet

## Design Trade-Offs

- Trade-Offs

- Xilinx specific IP cores in our ethernet and ADC modules

- Interfacing

- Migen to interface between each subcomponent

- Jupyter Notebook as our GUI.

- Resulting Actions

- Xilinx IP

- Decreased time to develop because the Xilinx IP due to modification

- Reduces the effectiveness of our overall project in CASPER's open-source environment.

- Migen

- Swapping out a proven & known project compilation for an unproven technology

- Potentially reduces development time if successful & increases if not

### Conceptual Sketch - CASPER spectrometer

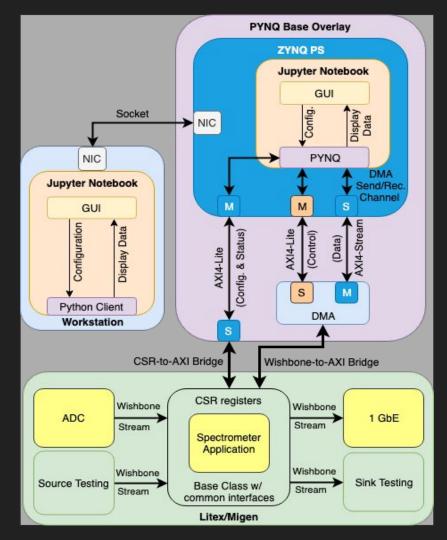

# Functional Block Diagram

### System Architecture

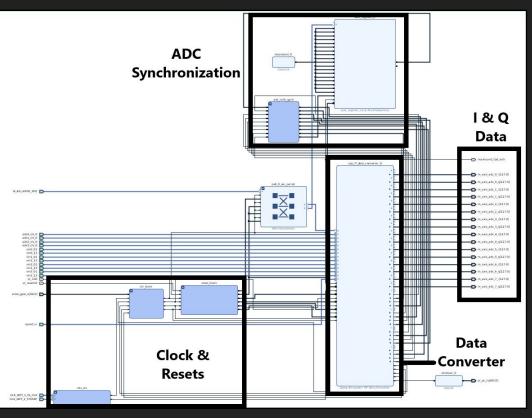

# ADC - Design & Implementation

- Purpose & Goal

- Initial desired spectrum: o 100 MHz

- Provide In-phase & Quadrature (I&Q) data to spectrometer

- Synchronous sampling for all ADC cores

Sdmay19-41 ADC Design

# ADC - Design & Implementation

- System Parameters

- Sampling Frequency: 256 MHz

- Multi-Tile Synchronized ADC Sampling

- 8-bit I&Q data streams from each ADC core

- Driven externally by ZYNQ PS

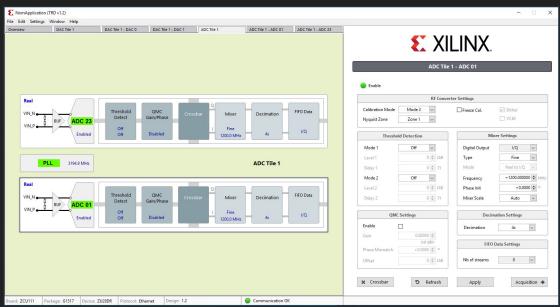

#### Xilinx GUI ADC Configuration

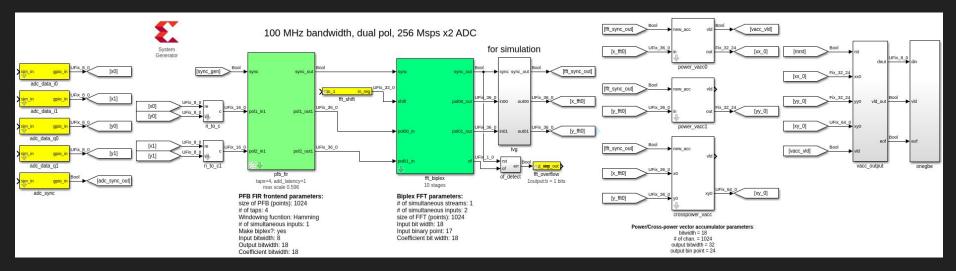

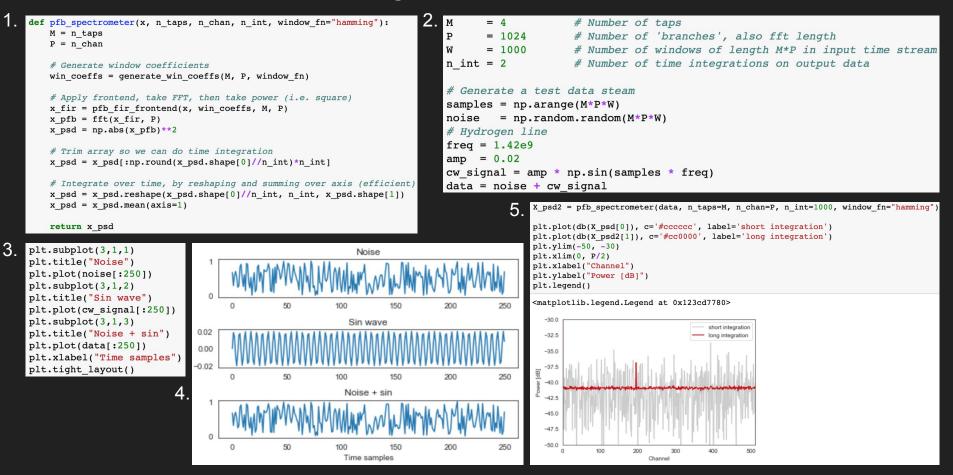

### Spectrometer - Design & Implementation

- Derived from Polyphase Filterbank-based (PFB) Simulink application for Allen Telescope Array in Northern California

- Used existing CASPER Toolflow's Simulink DSP libraries

- Created interactive Jupyter Notebook to simulate various DSP parameters

- Used Xilinx/MATLAB System Generator to generate corresponding HDL code

- Wrapped and instantiated inside of a Migen module with configuration and status registers

- Consulted with Jack Hickish regarding DSP parameters

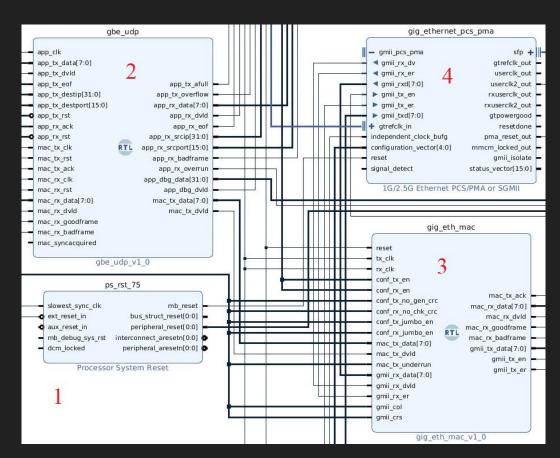

# Ethernet - Design & Implementation

- 10 GbE to 1GbE

- Merging CASPER IP with Xilinx IP

- 8-Bit data stream with 1 Gigabit speed

- Transmit only

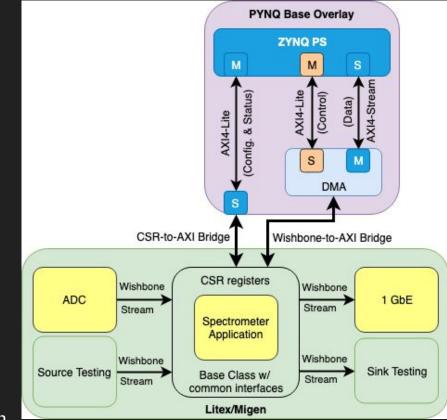

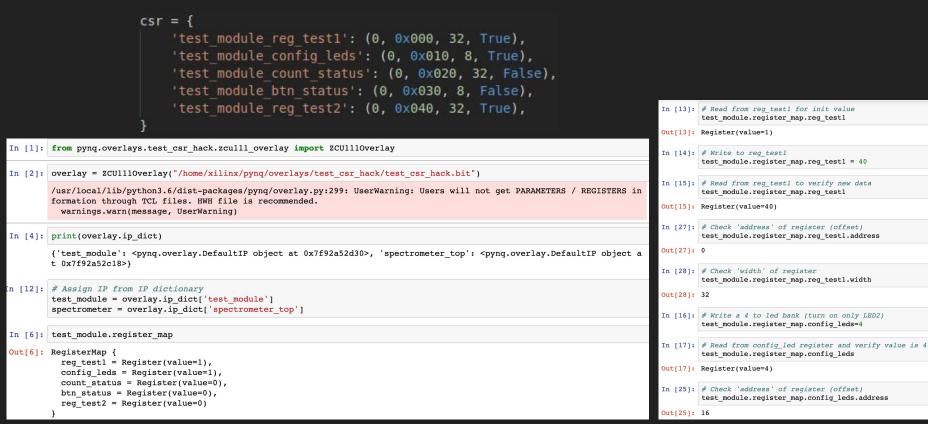

# **Build Environment - Design & Implementation**

- Litex/Migen build environment:

- Open-source FPGA design/SoC builder used to create cores and full FPGA designs.

- Fully-automated build process

- CSR Banks/buses

- CSR-to-AXI4-Lite bridge

- Migen Base Class

- Common CSR bus for config/status

- Wishbone Stream input & output

- PYNQ base overlay

- Exposes 3x AXI4-Lite interfaces

- Zynq Processing System

- DMA IP core with AXI4-Stream

\*Please chat with me more about this at poster presentation

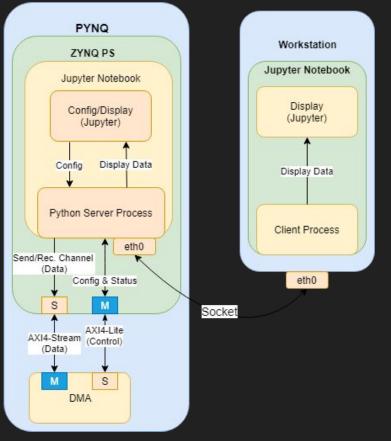

# GUI - Design & Implementation

- Requirements

- Sample data from the DMA IP core, and plot the data on Jupyter Notebooks

- Establish communication between Python

Server and Client process using sockets

- Send commands from the client process and respond with sampled data from the DMA IP to the client

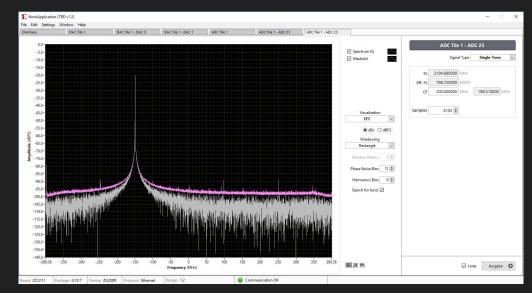

# ADC - Testing & Validation

- Verified Xilinx TRD

- Targeted Reference Design

- Validated target sampling parameters w/ TRD

- Collected parameter memory offsets to be tested w/ PYNQ

TRD ADC Data Capture w/ FFT

### ADC - Testing & Validation

#### Xilinx Data Converter IP Parameters

| entation 🌣 Presets | IP Location               |                               |                                         |               |                                         |           |   |

|--------------------|---------------------------|-------------------------------|-----------------------------------------|---------------|-----------------------------------------|-----------|---|

| bol ADC Physica    | al Resources │DAC P 4 ▶ ≣ | Component Name usp_rf_data_co | onverter_0                              |               |                                         |           |   |

| v disabled ports   |                           | P                             |                                         |               |                                         |           |   |

|                    |                           | Basic Advanced                |                                         |               |                                         |           |   |

|                    |                           | PLL and Clocking Configu      | ration                                  |               |                                         |           |   |

| + s_axi            | m00_axis 🕂 🗮              | ✓ Enable PLL                  |                                         |               |                                         |           |   |

| + adc0_clk         | m01_axis 🕂 🧮              |                               |                                         |               |                                         |           |   |

| + adc1_clk         | m02_axis 🕂 🧮              | Sampling Rate (GSPS)          | 4.096                                   | [1.0 - 4.096] | Clock Out (MHz)                         | 256.000   | ~ |

| In adc2_clk        | m03_axis 🕂 🧮              | Reference Clock (MHz)         | 512.000 🗸                               |               | AXI4-Stream Clock (MH:                  | 256.000   |   |

| In adc3_clk        | m10_axis 🕂 🧮              |                               |                                         |               |                                         |           |   |

| ► vin0_01          | m11_axis 🕂 🧮              |                               |                                         |               |                                         |           |   |

| ► vin0_23          | m12_axis 🕂 🧮              | Multi Tile Sync               | Link Coupling                           |               |                                         |           |   |

| ► vin1_01          | m13_axis 🕂 🧮              | ✓ Enable Multi Tile Syn       | Link Couplin                            | a AC 🗸        |                                         |           |   |

| ► vin1_23          | m20_axis 🕂 🧮              |                               | -                                       |               |                                         |           |   |

| ► vin2_01          | m21_axis 🕂 📃              | Converter Configuration       |                                         |               |                                         |           |   |

| ► vin2_23          | m22_axis 🕂 🧮              |                               |                                         |               |                                         |           |   |

| ► vin3_01          | m23_axis 🕂 🧮              | ADC 0                         |                                         | AD            | 1                                       |           |   |

| <b>↓</b> vin3_23   | m30_axis 🕂 🧮              | ✓ Enable ADC Invert Q Output  |                                         |               |                                         |           |   |

| ► sysref_in        | m31_axis 🕂 🧮              | ✓ Dither                      |                                         |               |                                         |           |   |

| s_axi_aclk         | m32_axis 🕂 🗮              |                               |                                         |               |                                         |           |   |

| s_axi_aresetn      | m33_axis 🕂 🧮              | Data Settings                 |                                         |               | Data Settings                           |           |   |

| user_sysref_adc    | adc0_calibration +        | Digital Output Data           | I/Q                                     | *             | Digital Output Data                     | I/Q       | × |

| m0_axis_aresetn    | adc1_calibration +        | Decimation Mode               | 2x                                      | ~             | Decimation Mode                         | 2x        | ~ |

| m0_axis_aclk       | adc2_calibration +        | Samples per AXI4-S            | tream Cycle 8                           | ~             | Samples per AXI4-Strea                  | m Cycle 8 | ~ |

|                    | adc3_calibration +        |                               | Required AXI4-Stream clock: 256.000 MHz |               | Required AXI4-Stream clock: 256.000 MHz |           |   |

| m1_axis_aclk       | clk_adc0 🗕                |                               |                                         |               |                                         |           |   |

| m2_axis_aresetn    | clk_adc1 🗕                | Mixer Settings                |                                         | 8             | Mixer Settings                          |           |   |

| m2_axis_aclk       | clk_adc2 🗕                | Mixer Type                    | Fine                                    | ~             | Mixer Type                              | Fine      | ~ |

| m3 axis aresetn    | clk_adc3 🛏                | Mixer Mode                    | Real->I/Q                               | ×             | Mixer Mode                              | Real->I/Q | ~ |

|                    |                           |                               |                                         |               |                                         |           |   |

| m3_axis_aclk       | irq 🗕                     | NCO Frequency (GF             | 0.0                                     | 0             | NCO Frequency (GHz)                     | 2.0       | 0 |

### ADC - Risks & Mitigation

- Inability to finish due to:

- Limited time

- Lack of expertise

- Pivot from 8 core ADC design to 2 Core ADC design

- Mitigation of risks

- Reach out to industry experts for help & guidance

### **Spectrometer - Testing & Validation**

- 1. Created a Jupyter Notebook to simulate and verify the DSP parameters necessary for 100 MHz spectrometer design

- 2. Simulated in Simulink by generating white-noise, injecting a signal and feeding the samples to the fully implemented spectrometer design made with CASPER's Simulink/MATLAB DSP libraries

- 3. Read/write the input/output data for the spectrometer component from/to DMA using PYNQ:

- a. Generate a sampled signal using numpy in PYNQ, write to DMA, read from DMA in hardware and feed to spectrometer HDL

- b. Write the spectrum to DMA in hardware, read spectral data from DMA in PYNQ and display plot to verify

- \* Was unable to complete #3 as DMA infrastructure was not completed in time

### **Spectrometer - Testing & Validation**

### Ethernet - Testing & Validation

- Implementation Choice

- Loopback Testing

- MicroBlaze Testing

- Sample Data Testing

- Current Progress

### Ethernet - Risks & Mitigation

- 10 GbE import

- Xilinx IP Licensing

- Using other CASPER IP

- Clocking and IP documentation

### **Build Environment - Testing & Validation**

\* Please refer to our demo during the poster presentation this afternoon for more information

### GUI - Testing & Validation

- Server and Client

- Generating signals by passing them to one server thread and the other to a client thread waiting to verify that data is being transmitted.

- The client process was tested by verifying data that was set with certain values based on user input.

- Control surfaces with a client process to connect to a server process, which would then write to GPIO control registers.

- Generating signals

- Numpy was then used to generate signals that will be passed to two FIR filters and the times compared.

### GUI - Risks and Mitigation

- GNURadio (Later switched to Jupyter Notebook)

- PYNQ readily supports Jupyter Notebook

- Notebook modules that allow data visualization

- Easier to configure data using ipywidgets and json for storing configurations

- Ability to read PYNQ registers through PYNQ modules

- Expertise

- Time

### **Roles & Responsibilities**

- Brian Bradford FPGA/DSP Engineer

- Build Environment (Migen/Litex)

- PYNQ

- Spectrometer application

- Louis Hamilton FPGA Engineer and GUI developer

- GUI design & implementation

- PYNQ DMA

- Jared Danner FPGA Engineer

- ADC Design & Implementation

- ZCU111 Migen Platform File

- Nick Knuth FPGA Engineer

- □ 1/10 GbE core

- Vishal Joel GUI Developer and FPGA Engineer

- GUI design & implementation

### **Project Schedule - Proposed**

### **Project Schedule - Actual**

### Lessons Learned

- Time required for FPGA development

- Technical knowledge necessary and gained

- Experience with unfamiliar technology

- Overcoming unforeseen risks and challenges

- Adapting to major changes in design

# Conclusions & Future Work

- Were not able to fully implement and test 100 MHz spectrometer on ZCU111

- Mostly rookie FPGA Engineers

- Time constraints

- Unforeseen risks regarding each module (explained earlier)

- Demonstrated potential to migrate to a fully open-source toolflow

- Automated build environment: Migen and PYNQ

- Substantial leg-work done for creation of CASPERized:

- ADC core

- 1 GbE core

- Code to be stored in Brian Bradford's GitHub & will notify CASPER community about location and progress

- Half a dozen or more members interested in expanding on our work

- Brian to give talk regarding project at CASPER 2019 conference in Boston

# Key Industry Consultants

- *Dan Werthimer:* Chief Scientist, SETI@Home, UC Berkeley Space Sciences Lab: <u>danw@ssl.berkeley.edu</u>

- Jack Hickish: Assistant Researcher, UC Berkeley Radio Astronomy Lab: jackhickish@ssl.berkeley.edu

- *Alan Wilson-Langman:* Senior Project Engineer, Vermeer Corporation: <u>awilson-langman@vermeer.com</u>

### Advisor

• Dr. Phillip Jones: Associate Professor, Department of Electrical and Computer Engineering, Iowa State University: <u>phjones@iastate.edu</u>

### References

- 1. Casper-dsp.org. (2018). The Collaboration for Astronomy Signal Processing and Electronics Research. [online] Available at: http://casper-dsp.org/ [Accessed 23 Oct. 2018].

- 2. M-labs.hk. (2018). Migen | M-Labs. [online] Available at: https://m-labs.hk/migen/index.html [Accessed 23 Oct. 2018].

- 3. Readthedocs.org. (2018). PYNQ | Read the Docs. [online] Available at: https://readthedocs.org/projects/pynq/ [Accessed 23 Oct. 2018].

- 4. leeexplore.ieee.org. (2018). Commissioning and testing of SERENDIP VI instrumentation USNC-URSI national radio science meeting IEEE Conference Publication. [online] Available at: https://ieeexplore.ieee.org/document/7436240/ [Accessed 23 Oct. 2018].

- 5. IEEE Std 211-1997<sup>™</sup> IEEE Standard Definitions of Terms for Radio Wave Propagation

- 6. IEEE Std 1241-2010<sup>™</sup> IEEE Standard of Terminology and Test Methods for Analog-to Digital Converters

- 7. IEEE Std 802.3<sup>™</sup> Standards for Ethernet

- 8. Price, D. (2018). Spectrometers and Polyphase Filterbanks in Radio Astronomy. [online] Arxiv.org. Available at: https://arxiv.org/abs/1607.03579 [Accessed 23 Oct. 2018].

- 9. Xilinx.com. (2018). [online] Available at: <u>https://www.xilinx.com/suppo</u>rt/documentation/application\_notes/xapp1305-ps-pl-based-ethernet-solution.pdf [Accessed 23 Oct. 2018].

- Xilinx.com. (2018). Zynq UltraScale+ RFSoC Data Converter. [online] Available at: https://www.xilinx.com/support/documentation/ip\_documentation/usp\_rf\_data\_converter/v2\_0/pg269-rf-data-converter.pdf [Accessed 23 Oct. 2018].

- 11. Hickish, J (2018). Allen Telescope Array: SNAP firmware. [online] Available at: https://github.com/realtimeradio/ata\_snap [Accessed 8 Jan. 2019].

- 12. Price, D (2017). Polyphase filterbanks: an interactive introduction. [online] Available at: https://github.com/telegraphic/pfb\_introduction [Accessed 12 Feb. 2019]

- 13. fpgadeveloper.com (2018). [online] Available at: http://www.fpgadeveloper.com/2018/03/how-to-accelerate-a-python-function-with-pynq.html [Accessed 1 Feb. 2019]